在人工智慧(AI)與高效能運算(HPC)呈現爆發式增長的當下,記憶體頻寬(Memory Bandwidth)已成為制約運算效能的關鍵瓶頸。作為行業標準制定者的 JEDEC 固態技術協會,近期正緊鑼密鼓地制定一項全新的記憶體標準:「SPHBM4」(Standard Package HBM4,標準封裝第四代高頻寬記憶體),期望能有接近 HBM 的速度但成本能遠低於傳統 CoWoS 封裝的選擇。

頻寬與面積的拉鋸戰:SPHBM4 的技術突破

長期以來,HBM(High Bandwidth Memory)憑藉其超高的傳輸位元寬度(Bit Width)稱霸高效能運算領域。傳統 HBM 記憶體通常採用 1024-bit 甚至 2048-bit 的位寬介面,這種設計雖然帶來了無可匹敵的傳輸效能與能效比,但也付出了昂貴的代價。如此龐大的介面位寬,意味著記憶體顆粒需要佔用大量的晶片面積來佈局 I/O 觸點,這不僅限制了單顆晶片的堆疊數量和封裝容量,更進一步佔用了 AI 加速卡寶貴的基板空間,制約了運算集群的整體算力密度。

SPHBM4 的核心突破在於其對位元寬度的大膽削減與傳輸效率的補償。根據現有資料顯示,SPHBM4 引入了先進的「4:1 串列技術」(Serialization),將原本高達 2048-bit 的位寬大幅縮減至 512-bit。這一改變看似「降級」,實則是為了更高效的集成。

儘管通道數量減少了四分之三,但 SPHBM4 仍致力於實現與完整版 HBM4 同級別的總頻寬。這意味著其單一通道的數據傳輸速率必須大幅提升。雖然 JEDEC 尚未公開具體的技術細節,究竟是單純將傳輸時脈提升至原有的四倍(達到驚人的 32GT/s),還是引入了更高階的編碼調變方案(如 PAM4 等),但其目標十分明確:在保持極致效能的同時,大幅釋放晶片面積與控制器設計的複雜度。

封裝技術的「降維打擊」:告別昂貴的中介層

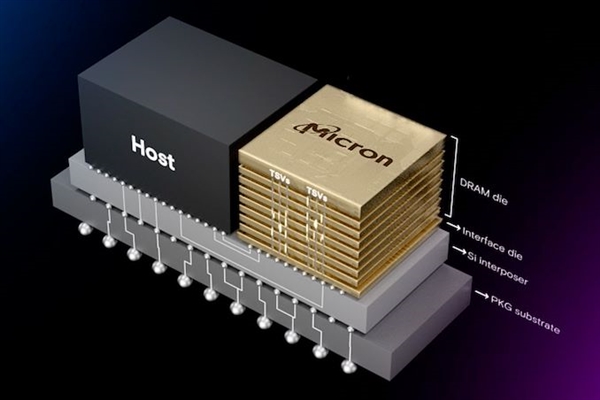

SPHBM4 最具革命性的意義,或許不在於速度,而在於其對封裝成本的控制。現有的 HBM 技術之所以昂貴且產能受限,很大程度上歸因於其對先進封裝技術的依賴。HBM 必須透過 CoWoS(Chip on Wafer on Substrate)這類 2.5D 封裝技術,利用昂貴的矽中介層(Silicon Interposer)與 GPU 或 ASIC 進行連接。這不僅拉高了製造成本,更受限於台積電等晶圓代工廠的先進封裝產能。

相比之下,SPHBM4 的命名中包含了「Standard Package」(標準封裝)一詞,揭示了其最大的優勢:相容傳統有機基板。這意味著 SPHBM4 可以擺脫對昂貴矽中介層的絕對依賴,直接應用於標準的封裝流程中。

在封裝內部,SPHBM4 依然沿用了業界標準的基礎裸晶(Base Die)與 HBM4 裸晶(Core Die)進行堆疊。這種設計確保了單個堆疊的容量能夠看齊 HBM4 及 HBM4E 標準,最高可達 64GB。更重要的是,由於介面位寬的縮減,控制器的設計得以簡化,整體封裝結構更加精簡。理論上,由於 I/O 佔用的面積減少,SPHBM4 甚至擁有比標準 HBM4 更高的潛在容量密度,甚至可達到 HBM4 的四倍之多,這對於極度渴求大容量記憶體的 AI 推論(Inference)模型來說,無疑是一大福音。

市場定位:精準填補生態系空白

從產品定位來看,SPHBM4 並非是為了取代處於金字塔頂端的 HBM4,而是為了填補市場的巨大真空。目前的記憶體市場呈現兩極化:一端是成本較低但頻寬有限的傳統 DDR5/LPDDR5;另一端則是性能極致但價格高昂、產能緊缺的 HBM3E/HBM4。在這兩者之間,存在著大量對頻寬有一定要求,但對成本也相當敏感的應用場景,例如中階 AI 推論伺服器、邊緣運算設備、以及部分高效能網路交換設備。

SPHBM4 的出現,正是為了成為介於傳統 DDR 與新型 HBM 之間的「第三種選擇」。它提供了遠超 DDR5 的頻寬,同時將整合成本控制在比標準 HBM 更親民的水準。

SPHBM4 不會取代 GDDR 顯存?

面對這樣一款「高頻寬、相對低成本」的記憶體,許多科技愛好者不禁會聯想到:它是否會取代顯示卡(Graphics Card)上的 GDDR6 或 GDDR7 顯存,成為新一代的遊戲顯存標準,讓遊戲顯卡更快、容量更大、更便宜??

從技術與經濟角度分析,答案顯然是「否定」的。

首先,設計目標的本質差異決定了其應用場景。SPHBM4 的首要任務是維持「HBM 等級的頻寬」與「高容量密度」,而非極致的成本控制。儘管它比標準 HBM4 便宜,去除了昂貴的中介層,但其本質依然是基於 TSV(矽通孔)技術的 3D 堆疊記憶體。

這意味著,SPHBM4 的製造過程仍需涉及複雜的晶圓級堆疊工藝、基片接口匹配以及先進的散熱處理解決方案。相比之下,GDDR 記憶體採用的是相對成熟的平面封裝技術,其成本效益極高,且專為消費級圖形處理進行了優化。

若在消費級顯示卡上強行導入 SPHBM4,雖然能減少顆粒數量(例如用一顆 SPHBM4 取代多顆 GDDR),但單顆 SPHBM4 的成本依然遠高於多顆 GDDR 的總和。此外,為了適配 SPHBM4,GPU 核心的記憶體控制器與封裝基板也需重新設計,這將導致整張顯示卡的 BOM(物料清單)成本不降反升。

因此,SPHBM4 在成本上無法降至 GDDR 的級別,在性能提升上對於遊戲場景而言性價比不高。它注定是為了解決運算中心的算力瓶頸而生,而非為了提升遊戲玩家的幀數。

SPHBM4 預計將在未來的 AI 推論卡、高階網路晶片以及次旗艦級 HPC 加速器中大放異彩。但它不會取代 HBM 在頂級訓練晶片中的地位,也不會動搖 GDDR 在消費電子領域的統治,但它將作為一座堅實的橋樑,連結起頻寬與成本的兩端,加速 AI 運算在更多層級市場的普及與落地。